# Systems I: Computer Organization and Architecture

Lecture 9 - Register Transfer and Microoperations

# Microoperations

- Digital systems are modular in nature, with modules containing registers, decoders, arithmetic elements, control logic, etc.

- These digital components are defined by the registers that they contain and the operations performed on their data. These operations are called microoperations.

- Microoperations are elementary operations performed on the information stored in one or more registers.

# Hardware Organization

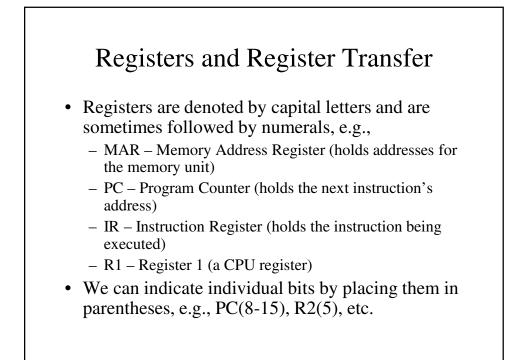

- The hardware organization of a digital computer is best defined by specifying:

- The set of register that it contains and their function.

- The sequence of microoperations performed on the binary information stored in the registers.

- The control signals that initiates the sequence of microoperations.

| R1                | 7 6 5 4 3 2 1 0         |

|-------------------|-------------------------|

| Register R        | Showing Individual Bits |

| RI                | PC(H) PC(L)             |

| Numbering of Bits | Divided Into Two Parts  |

|                        | C                                  |                                      |

|------------------------|------------------------------------|--------------------------------------|

| Symbol                 | Description                        | Examples                             |

| Letters (and numerals) | Denotes a register                 | MAR, R2                              |

| Parentheses ()         | Denotes a part<br>of a register    | R2(0-7), R2(L)                       |

| Arrow $\rightarrow$    | Denotes Transfer<br>of information | $R2 \leftarrow R1$                   |

| Comma ,                | Separates 2<br>microoperations     | $R2 \leftarrow R1, R1 \leftarrow R1$ |

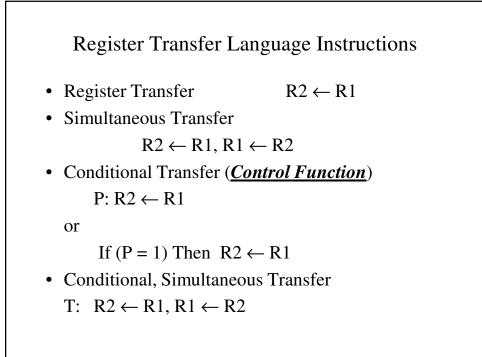

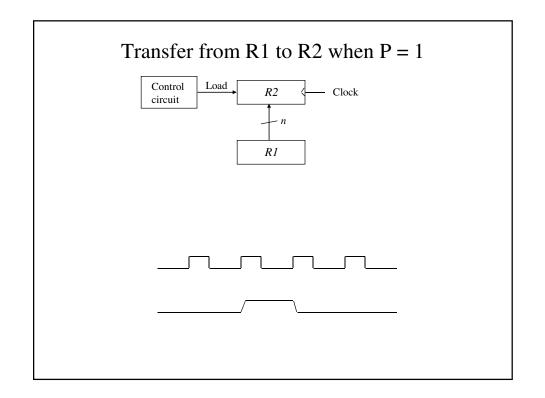

The statement P: R2 ← R1 implies the existence of the necessary circuitry to implement the transfer as well as the mechanism to set and clear the control variable P.

### The Bus

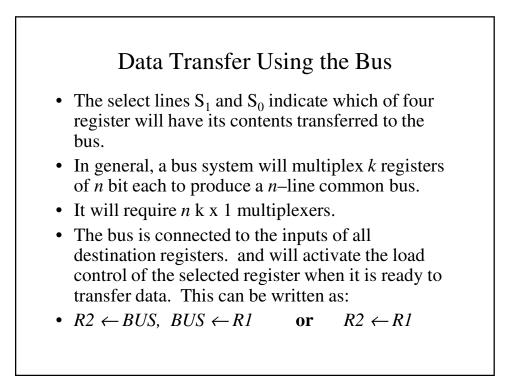

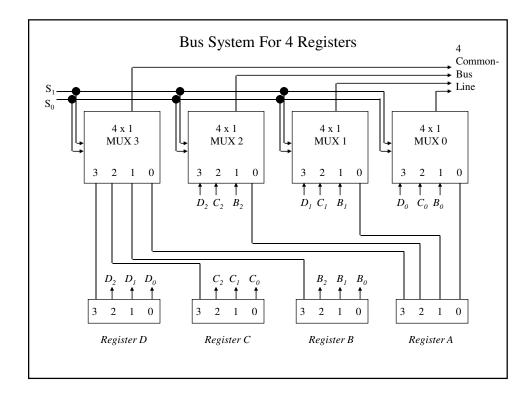

- A bus is a set of common wires that carries data between registers.

- There is a separate wire for every bit in the registers.

- There are also a set of control signals which determines which register is selected by the bus at a particular time.

- A bus can be constructed using multiplexer which enable a sets of registers to share a common bus for data transfer.

| Functio    | n Table f             | or the Bus                      |

|------------|-----------------------|---------------------------------|

| <u>S</u> 1 | <u>S</u> <sub>0</sub> | <b><u>Register Selected</u></b> |

| 0          | 0                     | A                               |

| 0          | 1                     | В                               |

| 1          | 0                     | C                               |

| 1          | 1                     | D                               |

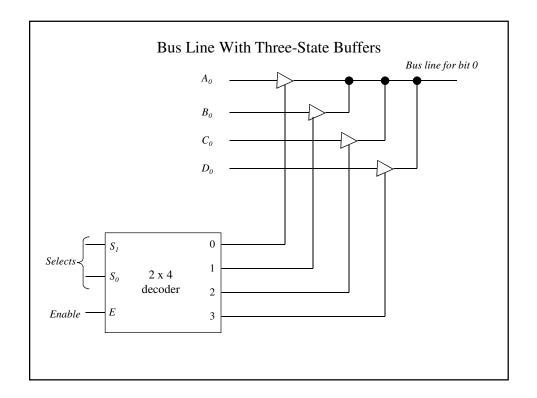

### Three State-Bus Buffers

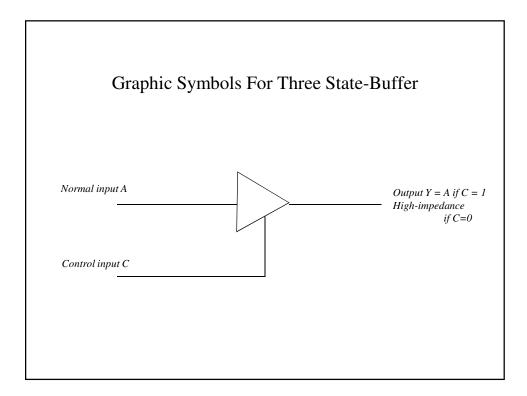

- A bus can be built using three-state buffers instead of multiplexers.

- A three-state gate has three states: 1, 0 and a highimpedance state, which behaves like an open circuit.

- It is possible to connect a large number of threestate gates in a common bus line without overloading it.

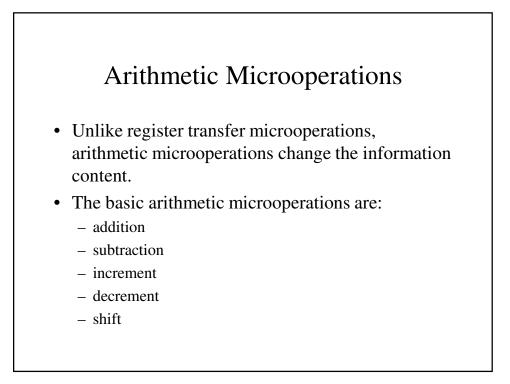

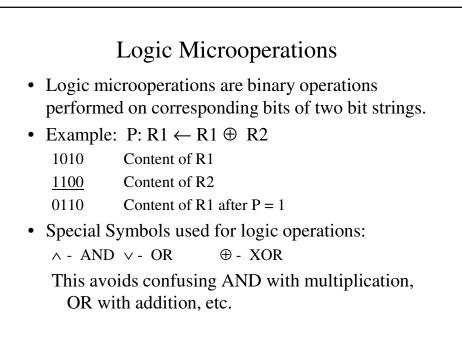

### Microoperations

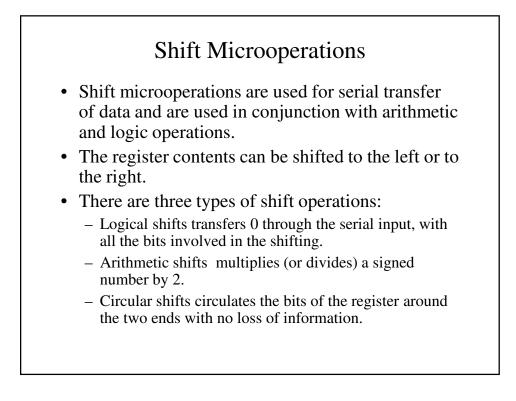

- Microoperations are classified into four categories:

- Register transfer microoperations (data moves from register to register)

- Arithmetic microoperations (perform arithmetic on data in registers)

- Logic microoperations (perform bit manipulation on data in registers)

- Shift microoperations (perform shift on data in registers)

#### Arithmetic Microoperations (continued)

• The RTL statement:

$\text{R3} \leftarrow \text{R1} + \text{R2}$

indicates an add microoperation. We can similarly specify the other arithmetic microoperations.

- Multiplication and division are not considered microoperations.

- Multiplication is implemented by a sequence of adds and shifts.

- Division is implemented by a sequence of substracts and shifts.

| <u>Symbolic</u>                        | Description                               |

|----------------------------------------|-------------------------------------------|

| <b>Designation</b>                     |                                           |

| $R3 \leftarrow R1 + R2$                | Contents of R1 plus R2 transferred to R3  |

| $R3 \leftarrow R1 - R2$                | Contents of R1 minus R2 transferred to R3 |

| $R2 \leftarrow \overline{R2}$          | Complement contents of R2 (1's comp.)     |

| $R2 \leftarrow \overline{R2} + 1$      | 2's complment contens of R2 (negate)      |

| $R3 \leftarrow R1 + \overline{R2} + 1$ | R1 plus 2's comp. of R2                   |

| $R1 \leftarrow R1 + 1$                 | Increment content of R1 by 1              |

| $R1 \leftarrow R1 - 1$                 | Decrement content of R1 by 1              |

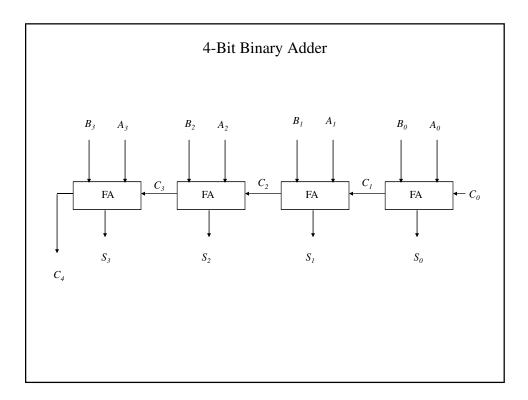

# Binary Adder We implement a binary adder with registers to hold the data and a digital circuit to perform the addition (called a *binary adder*). The binary adders is constructed using full adders connected in cascade so that the carry produced by one full adder becomes an input for the next. Adding two *n*-bit numbers requires *n* full adders. The *n* data bits for *A* and *B* might come from *R1* and *R2* respectively

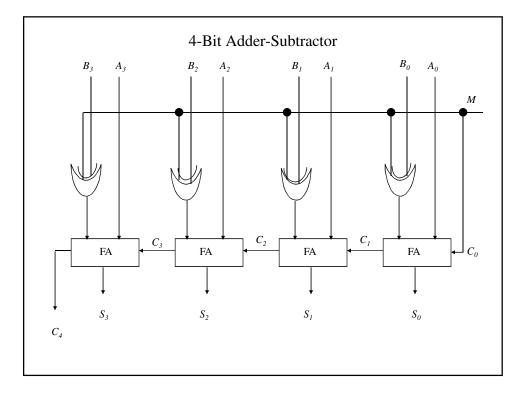

### Adder-Subtracter

- Subtracting A B is most easily done by adding B' to A and then adding 1.

- This makes it convenient to combine both addition and subtraction into one circuit, called an adder-subtracter.

- M is the mode indicator

- M = 0 indicates addition (B is left alone and  $C_0$  is 0)

- M = 1 indicates subtraction (B is complement and  $C_0$  is 1).

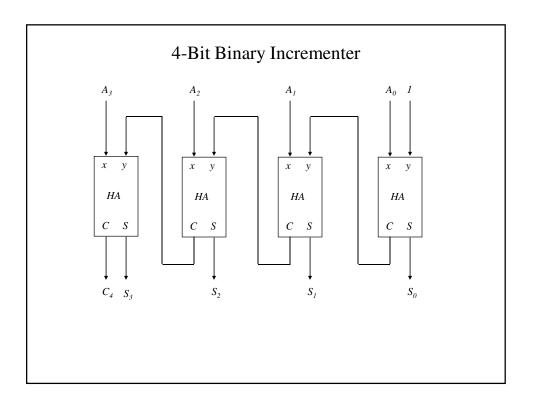

# Binary Incrementer

- The binary incrementer adds 1 to the contents of a register, e.g., a register storing 0101 would have 0110 in it after being incremented.

- There are times when we want incrementing done independent of a register. We can accomplish this with a series of cascading half-adders.

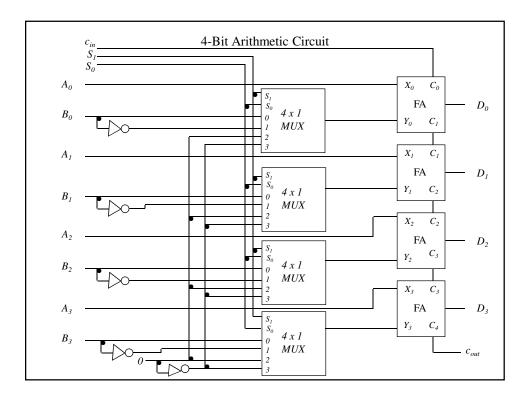

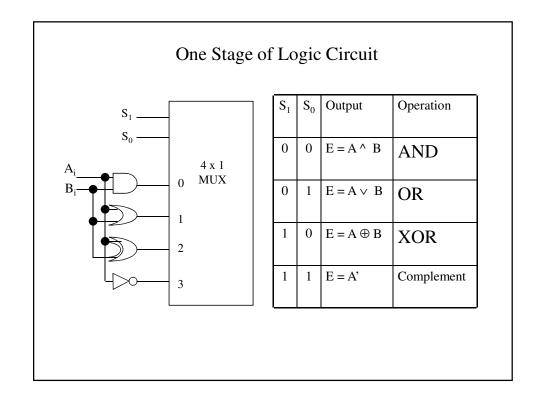

### Arithmetic Circuit

- We can implement 7 arithmetic microoperations (add, add with carry, subtract, subtract with borrow, increment, decrement and transfer) with one circuit.

- We provide a series of cascading full adders with A<sub>i</sub> and the output of a 4x1 multiplexer.

- The multiplexers' inputs are two selects, B<sub>i</sub>, B<sub>i</sub>', logical 0 and logical 1.

- Which of these four values we provide (together with the carry) determines which microoperation is performed.

|           | <u>Sele</u> | <u>ct</u> ] | Inpu | t <u>Output</u>                                                      |                       |

|-----------|-------------|-------------|------|----------------------------------------------------------------------|-----------------------|

| <u>S1</u> | <u>S</u> 0  | <u>C</u> in | Y    | $\underline{\mathbf{D} = \mathbf{A} + \mathbf{Y} + \mathbf{C}_{in}}$ | <b>Microoperation</b> |

| 0         | 0           | 0           | В    | $\mathbf{D} = \mathbf{A} + \mathbf{B}$                               | Add                   |

| 0         | 0           | 1           | В    | $\mathbf{D} = \mathbf{A} + \mathbf{B} + 1$                           | Add with Carry        |

| 0         | 1           | 0           | B    | $D = A + \overline{B}$                                               | Subtract with Borrow  |

| 0         | 1           | 1           | B    | $D = A + \overline{B} + 1$                                           | subtract              |

| 1         | 0           | 0           | 0    | D = A                                                                | Transfer A            |

| 1         | 0           | 1           | 0    | D = A + 1                                                            | Increment A           |

| 1         | 1           | 0           | 1    | $\mathbf{D} = \mathbf{A} - 1$                                        | Decrement A           |

| 1         | 1           | 1           | 1    | D = A                                                                | Transfer A            |

### The Microoperations of the Arithmetic Circuit

- When  $S_1S_0 = 00$ , the MUX provides B. The result is Add (for  $C_{in} = 0$ ) or Add With Carry (for  $C_{in} = 1$ ).

- When  $S_1S_0 = 01$ , the MUX provides B'. The result is Subtract with Borrow (for  $C_{in} = 0$ ) or Subtract (for  $C_{in} = 1$ ).

- When  $S_1S_0 = 10$ , the MUX provides 0. The result is Transfer (for  $C_{in} = 0$ ) or Increment (for  $C_{in} = 1$ ).

- When  $S_1S_0 = 11$ , the MUX provides 1. The result is Decrement (for  $C_{in} = 0$ ) or Transfer (for  $C_{in} = 1$ ).

| [ru      | th ] | Fable                 | es fo      | or 16      | 5 2-"                 | Vari       | able       | e Fui      | nctic      |

|----------|------|-----------------------|------------|------------|-----------------------|------------|------------|------------|------------|

| <u>X</u> | Y    | <u>F</u> <sub>0</sub> | <u>F</u> 1 | <u>F</u> 2 | <u>F</u> <sub>3</sub> | <u>F</u> 4 | <u>F</u> 5 | <u>F</u> 6 | <u>F</u> 7 |

| 0        | 0    | 0                     | 0          | 0          | 0                     | 0          | 0          | 0          | 0          |

| 0        | 1    | 0                     | 0          | 0          | 0                     | 1          | 1          | 1          | 1          |

| 1        | 0    | 0                     | 0          | 1          | 1                     | 0          | 0          | 1          | 1          |

| 1        | 1    | 0                     | 1          | 0          | 1                     | 0          | 1          | 0          | 1          |

| K | Y | <u>F</u> 8 | <u>F9</u> | <u><b>F</b></u> <sub>10</sub> | <u>F<sub>11</sub></u> | <u><b>F</b></u> <sub>12</sub> | <u><b>F</b></u> <sub>13</sub> | <u>F<sub>14</sub></u> | <u>F<sub>15</sub></u> |

|---|---|------------|-----------|-------------------------------|-----------------------|-------------------------------|-------------------------------|-----------------------|-----------------------|

| 0 | 0 | 1          | 1         | 1                             | 1                     | 1                             | 1                             | 1                     | 1                     |

| 0 | 1 | 0          | 0         | 0                             | 0                     | 1                             | 1                             | 1                     | 1                     |

| 1 | 0 | 0          | 0         | 1                             | 1                     | 0                             | 0                             | 1                     | 1                     |

| 1 | 1 | 0          | 1         | 0                             | 1                     | 0                             | 1                             | 0                     | 1                     |

|                         | n Logic Microop                      | crations     |

|-------------------------|--------------------------------------|--------------|

| <b>Boolean Function</b> | Microoperation                       | Name         |

| $F_0 = 0$               | $F \leftarrow 0$                     | Clear        |

| $F_1 = xy$              | $F \leftarrow A \land B$             | AND          |

| $F_2 = xy'$             | $F \leftarrow A \land \overline{B}$  |              |

| $F_3 = x$               | F←A                                  | Transfer A   |

| $F_4 = x'y$             | $F \leftarrow \overline{A} \wedge B$ |              |

| $F_5 = y$               | F←B                                  | Transfer B   |

| $F_6 = x \oplus y$      | $F \leftarrow A \oplus B$            | Exclusive-OR |

| $F_7 = x + y$           | $F \leftarrow A \lor B$              | OR           |

| <b>Boolean Function</b>                      | <b>Microoperation</b>                | Name           |

|----------------------------------------------|--------------------------------------|----------------|

| $F_8 = (x + y)'$                             | $F \leftarrow \overline{A \lor B}$   | NOR            |

| $F_9 = (x \oplus y)'$                        | $F \leftarrow \overline{A \oplus B}$ | Exclusive-NOR  |

| $F_{10} = y'$                                | $F \leftarrow \overline{B}$          | Complement B   |

| $\mathbf{F}_{11} = \mathbf{x} + \mathbf{y}'$ | $F \leftarrow A \lor \overline{B}$   |                |

| $F_{12} = x'$                                | $F \leftarrow \overline{A}$          | Complement A   |

| $F_{13} = x' + y$                            | $F \leftarrow \overline{A} \lor B$   |                |

| $F_{14} = (xy)'$                             | $F \leftarrow \overline{A \land B}$  | NAND           |

| $F_{15} = 1$                                 | $F \leftarrow all 1$ 's              | Set to all 1's |

### Logic Applications

- Logic Operations allow us to manipulate individual bits in ways that we could not do otherwise.

- These applications include:

- selective set

- selective complement

- select clear

- mask

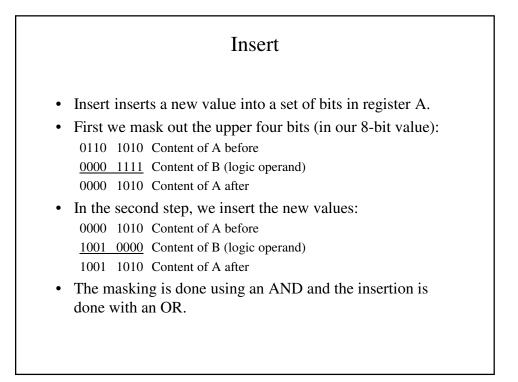

- insert

- clear

- 1 in register B:

- 1010 Content of A before

- <u>1100</u> Content of B (logic operand)

- 0110 Content of A after

- This is done using the exclusive-OR operation.

# Mask

- Mask clears to 0 the bits in register A where there is a corresponding 0 in register B:

- 1010 Content of A before

- <u>1100</u> Content of B (logic operand)

- 1000 Content of A after

- This is done using the logical-AND operation and **B**.

If A& B are both 1 or both 0, this produces 0. This is done using the logical-AND operation and **B**.

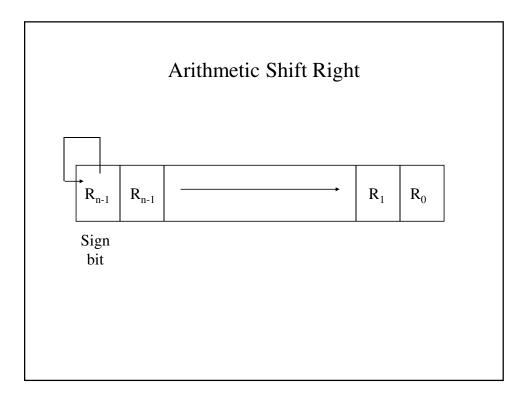

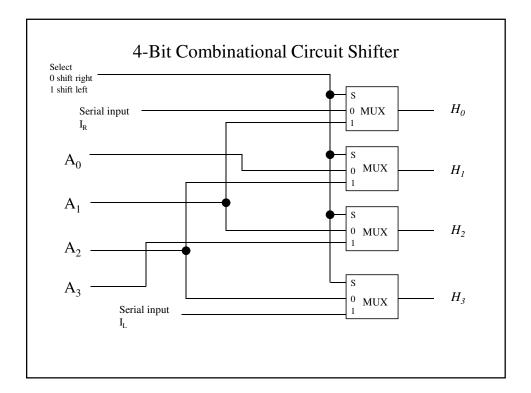

| Symbolic Designation   | Description                       |

|------------------------|-----------------------------------|

| $R \leftarrow shl R$   | Shift-left register R             |

| $R \leftarrow shr R$   | Shift-right register R            |

| $R \leftarrow cil R$   | Circular shift-left register R    |

| $R \leftarrow cir R$   | Circular shift-right register R   |

| $R \leftarrow ashl R$  | Arithmetic Shift-left register R  |

| $R \leftarrow a shr R$ | Arithmetic Shift-right register R |

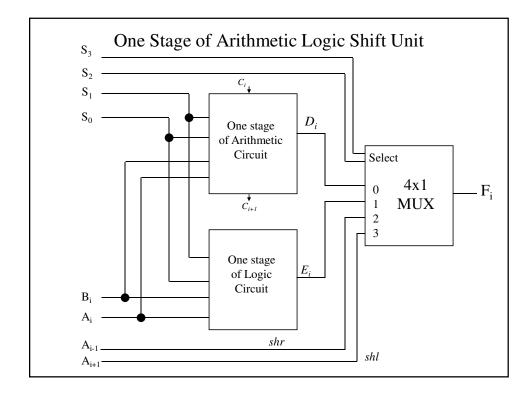

|            | <u>Op</u>  | eratio     | on Sele    | ect         |                                            |                      |

|------------|------------|------------|------------|-------------|--------------------------------------------|----------------------|

| <u>S</u> 3 | <u>S</u> 2 | <u>S</u> 1 | <u>S</u> 0 | <u>C</u> in | Operation                                  | Function             |

| 0          | 0          | 0          | 0          | 0           | F=A                                        | Transfer A           |

| 0          | 0          | 0          | 0          | 1           | $\mathbf{F} = \mathbf{A} + 1$              | Increment A          |

| 0          | 0          | 0          | 1          | 0           | F = A + B                                  | Addition             |

| 0          | 0          | 0          | 1          | 1           | $\mathbf{F} = \mathbf{A} + \mathbf{B} + 1$ | Add with Carry       |

| 0          | 0          | 1          | 0          | 0           | $F = A + \overline{B}$                     | Subtract with Borrow |

| 0          | 0          | 1          | 0          | 1           | $F = A + \overline{B} + 1$                 | Subtraction          |

| 0          | 0          | 1          | 1          | 0           | F = A - 1                                  | Decrement A          |

| 0          | 0          | 1          | 1          | 1           | F = A                                      | Transfer A           |

|            | <u>Ope</u> | ratio      | n Sele     | <u>ct</u>              |                  |                      |

|------------|------------|------------|------------|------------------------|------------------|----------------------|

| <u>S</u> 3 | <u>S</u> 2 | <u>S</u> 1 | <u>S</u> 0 | <u>C</u> <sub>in</sub> | Operation        | Function             |

| 0          | 1          | 0          | 0          | х                      | $F = A \wedge B$ | AND                  |

| 0          | 1          | 0          | 1          | x                      | $F = A \lor B$   | OR                   |

| 0          | 1          | 1          | 0          | x                      | $F = A \oplus B$ | XOR                  |

| 0          | 1          | 1          | 1          | х                      | F = A            | Complement A         |

| 1          | 0          | х          | х          | х                      | F = shr A        | Shift-Right A into F |

| 1          | 1          | х          | x          | х                      | F = shl A        | Shift-Left A into F  |