# Systems I: Computer Organization and Architecture

Lecture 10: Microprogrammed Control

## Microprogramming

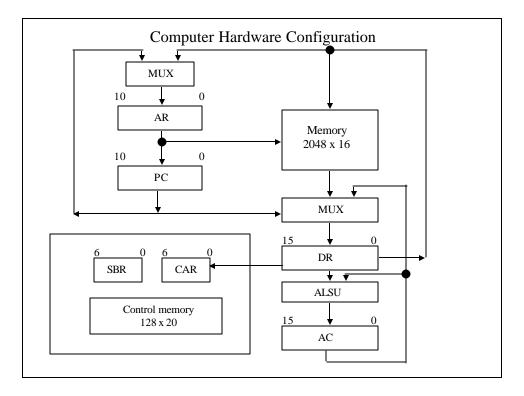

- The control unit is responsible for initiating the sequence of microoperations that comprise instructions.

- When these control signals are generated by hardware, the control unit is <u>hardwired</u>.

- When these control signals originate in data stored in a special unit and constitute a program on the small scale, the control unit is <u>microprogrammed</u>.

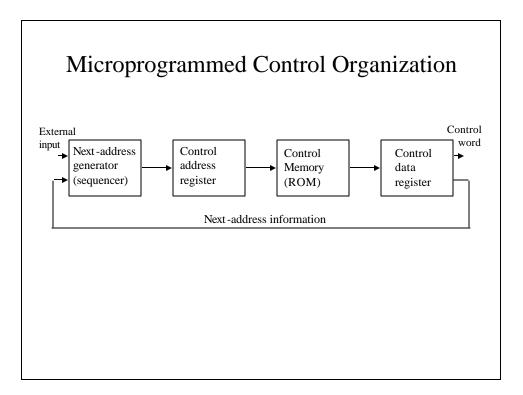

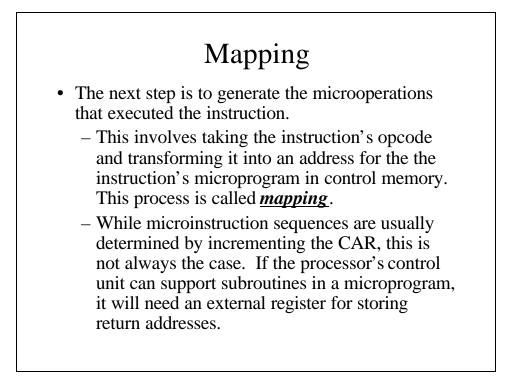

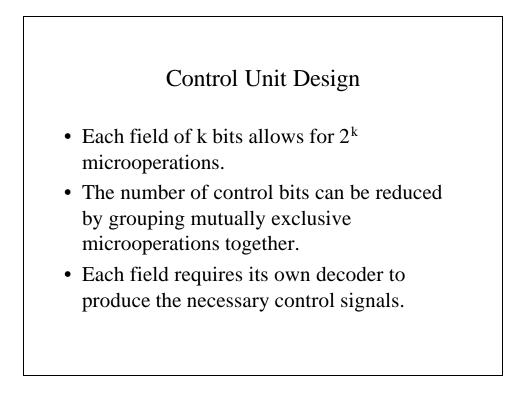

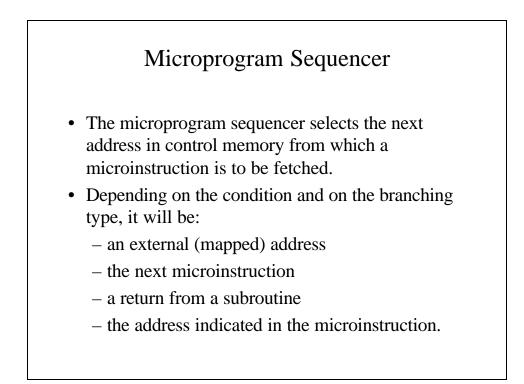

### Address Sequencing

- Microinstructions are usually stored in groups where each group specifies a routine, where each routine specifies how to carry out an instruction.

- Each routine must be able to branch to the next routine in the sequence.

- An initial address is loaded into the CAR when power is turned on; this is usually the address of the first microinstruction in the instruction fetch routine.

- Next, the control unit must determine the effective address of the instruction.

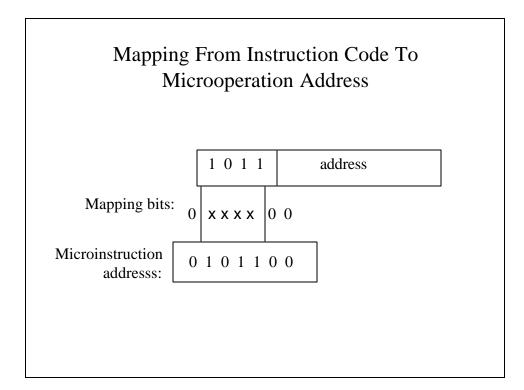

## **Conditional Branching**

- Status bits

- provide parameter information such as the carry-out from the adder, sign of a number, mode bits of an instruction, etc.

- control the conditional branch decisions made by the branch logic together with the field in the microinstruction that specifies a branch address.

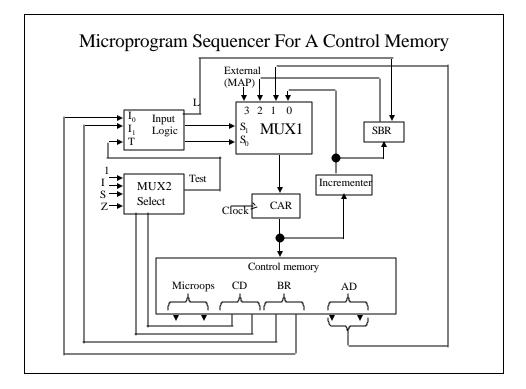

#### Branch Logic

- Branch Logic may be implemented in one of several ways:

- The simplest way is to test the specified condition and branch if the condition is true; else increment the address register.

- This is implemented using a multiplexer:

- If the status bit is one of eight status bits, it is indicated by a 3-bit select number.

- If the select status bit is 1, the output is 0; else it is 0.

- A 1 generates the control signal for the branch; a 0 generates the signal to increment the CAR.

- Unconditional branching occurs by fixing the status bit as always being 1.

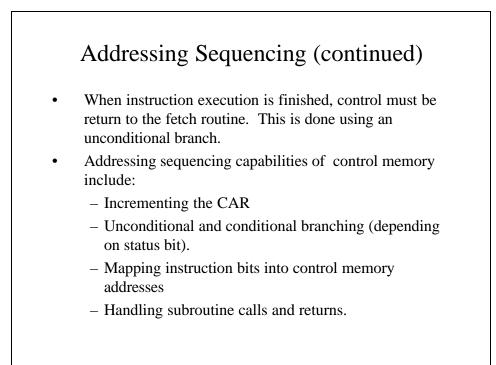

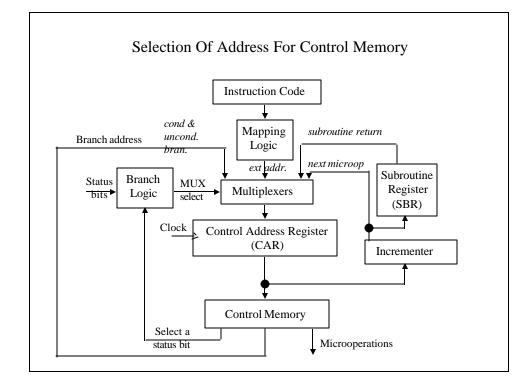

# Mapping of Instruction

- Branching to the first word of a microprogram is a special type of branch. The branch is indicated by the opcode of the instruction.

- The mapping scheme shown in the figure allows for four microinstruction as well as overflow space from 1000000 to 1111111.

| 15 14         | 11 10         |                                                 | ( |

|---------------|---------------|-------------------------------------------------|---|

| I Opcode      |               |                                                 |   |

| <u>Symbol</u> | <u>Opcode</u> | Description                                     |   |

| ADD           | 0000          | $AC \leftarrow AC + M[EA]$                      | _ |

| BRANCH        | 0001          | IF (AC > 0)<br>THEN PC $\leftarrow$ EA          | _ |

| STORE         | 0010          | M[EA] ← AC                                      |   |

| EXCHANGE      | 0011          | $AC \leftarrow M[EA],$<br>$M[EA] \leftarrow AC$ | - |

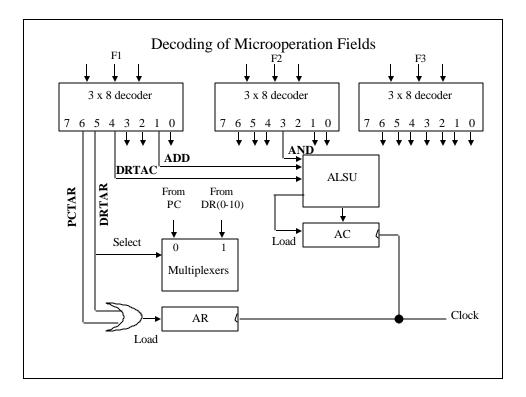

#### Symbols and Binary Code For Microinstruction Fields

| <u>F1</u> | <b>Microoperation</b>    | <u>Symbol</u> |

|-----------|--------------------------|---------------|

| 000       | None                     | NOP           |

| 001       | $AC \leftarrow AC + DR$  | ADD           |

| 010       | $AC \leftarrow 0$        | CLRAC         |

| 011       | $AC \leftarrow AC + 1$   | INCAC         |

| 100       | $AC \leftarrow DR$       | DRTAC         |

| 101       | $AR \leftarrow DR(0-10)$ | DRTAR         |

| 110       | $AR \leftarrow PC$       | PCTAR         |

| 111       | $M[AR] \leftarrow DR$    | WRITE         |

#### Symbols and Binary Code For Microinstruction Fields (continued)

| <u>F2</u> | <b>Microoperation</b>       | Symbol |  |  |

|-----------|-----------------------------|--------|--|--|

| 000       | None                        | NOP    |  |  |

| 001       | $AC \leftarrow AC - DR$     | SUB    |  |  |

| 010       | $AC \leftarrow AC \lor DR$  | OR     |  |  |

| 011       | $AC \leftarrow AC \land DR$ | AND    |  |  |

| 100       | $DR \leftarrow M[AR]$       | READ   |  |  |

| 101       | $DR \leftarrow AC$          | ACTDR  |  |  |

| 110       | $DR \leftarrow DR + 1$      | INCDR  |  |  |

| 111       | $DR(0-10) \leftarrow PC$    | PCTDR  |  |  |

| Symbols and Binary Code For         |

|-------------------------------------|

| Microinstruction Fields (continued) |

| <u>F3</u> | <b>Microoperation</b>        | <u>Symbol</u> |

|-----------|------------------------------|---------------|

| 000       | None                         | NOP           |

| 001       | $AC \leftarrow AC \oplus DR$ | XOR           |

| 010       | $AC \leftarrow AC'$          | СОМ           |

| 011       | $AC \leftarrow shl AC$       | SHL           |

| 100       | $AC \leftarrow shr AC$       | SHR           |

| 101       | $PC \leftarrow PC + 1$       | INCPC         |

| 110       | $PC \leftarrow AR$           | ARTPC         |

| 111       | Reserved                     |               |

#### Symbols and Binary Code For Microinstruction Fields (continued)

| <u>CD</u> | <b>Condition</b> | <u>Symbol</u> | <u>Comments</u>         |

|-----------|------------------|---------------|-------------------------|

| 00        | Always = 1       | U             | Unconditional<br>Branch |

| 01        | DR(15)           | Ι             | Indirect Address<br>bit |

| 10        | AC(15)           | S             | Sign bit of AC          |

| 11        | AC = 0           | Z             | Zero value in AC        |

| <u>BR</u> | <u>Symbol</u> | <b>Function</b>                                                                                                       |

|-----------|---------------|-----------------------------------------------------------------------------------------------------------------------|

| 00        | JMP           | $CAR \leftarrow AR \text{ if condition} = 1$ $CAR \leftarrow CAR + 1 \text{ if condition} = 0$                        |

| 01        | CAL           | $CAR \leftarrow AR, SBR \leftarrow CAR + 1 \text{ if cond.} = 1$<br>$CAR \leftarrow CAR + 1 \text{ if condition} = 0$ |

| 10        | RET           | $CAR \leftarrow SBR$ (return from subroutine)                                                                         |

| 11        | MAP           | $CAR(2-5) \leftarrow DR(11-14), CAR(0, 1, 6) \leftarrow 0$                                                            |

#### Symbolic Microinstructions

- It is possible to create a symbolic language for microcode that is machine-translatable to binary code.

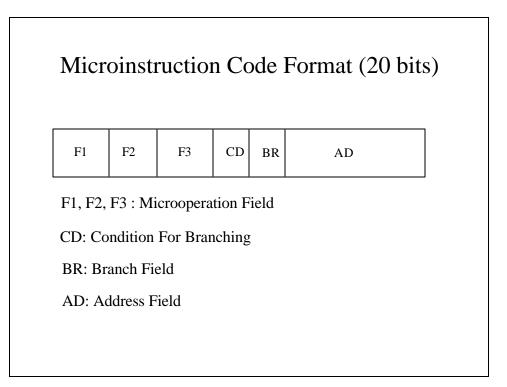

- Each line define a symbolic microinstruction with each column defining one of five fields:

- **Label** Either blank or a name followed by a colon (*indicates a potential branch*)

- <u>Microoperations</u> One, Two, Three Symbols, separated by commas (*indicates that the microoperation being performed*)

- <u>**CD</u>** Either U, I, S or Z (*indicates condition*)</u>

- **<u>BR</u>** One of four two-bit numbers

- <u>AD</u> A Symbolic Address, NEXT (address), RET, MAP (both of these last two converted to zeros by the assembler) (*indicates the address of the next microinstruction*)

- We will use the pseudoinstruction ORG to define the first instruction (or origin) of a microprogram, e.g., ORG 64 begins at 1000000.

| Label   | Microoperat | tions CD | BR   | AD     |

|---------|-------------|----------|------|--------|

|         | ORG 0       |          |      |        |

| ADD:    | NOP         | Ι        | CALL | INDRCT |

|         | READ        | U        | JMP  | NEXT   |

|         | ADD         | U        | JMP  | FETCH  |

|         | ORG 4       |          |      |        |

| BRANCH: | NOP         | S        | JMP  | OVER   |

|         | NOP         | U        | JMP  | FETCH  |

| OVER:   | NOP         | Ι        | CALL | INDRCT |

|         | ARTPC       | U        | JMP  | FETCH  |

|         | ORG 8       |          |      |        |

| STORE:  | NOP         | Ι        | CALL | INDRCT |

|         | ACTDR       | U        | JMP  | NEXT   |

|         | WRITE       | U        | JMP  | FETCH  |

|           | ORG 12      |    |      |        |

|-----------|-------------|----|------|--------|

| EXCHANGE: | NOP         | Ι  | CALL | INDRCT |

|           | READ        | U  | JMP  | NEXT   |

|           | ARTDR, DRTA | CU | JMP  | NEXT   |

|           | WRITE       | U  | JMP  | FETCH  |

|           | ORG 64      |    |      |        |

| FETCH:    | PCTAR       | U  | JMP  | NEXT   |

|           | READ, INCPC | U  | JMP  | NEXT   |

|           | DRTAC       | U  | MAP  |        |

| INDRCT:   | READ        | U  | JMP  | NEXT   |

|           | DRTAC       | U  | RET  |        |

|          | Add     | iress   |     | Bin | ary Mid | roinst | ructio | n       |

|----------|---------|---------|-----|-----|---------|--------|--------|---------|

| Micro-   |         |         |     |     |         |        |        |         |

| Routine  | Decimal | Binary  | F 1 | F2  | F3      | CD     | BR     | AD      |

| ADD      | 0       | 0000000 | 000 | 000 | 000     | 01     | 01     | 1000011 |

|          | 1       | 0000001 | 000 | 100 | 000     | 00     | 00     | 0000010 |

|          | 2       | 0000010 | 001 | 000 | 000     | 00     | 00     | 1000000 |

|          | 3       | 0000011 | 000 | 000 | 000     | 00     | 00     | 1000000 |

| BRANCH   | 4       | 0000100 | 000 | 000 | 000     | 10     | 00     | 0000110 |

|          | 5       | 0000101 | 000 | 000 | 000     | 00     | 00     | 1000000 |

|          | 6       | 0000110 | 000 | 000 | 000     | 01     | 01     | 100001  |

|          | 7       | 0000111 | 000 | 000 | 110     | 00     | 00     | 1000000 |

| STORE    | 8       | 0001000 | 000 | 000 | 000     | 01     | 01     | 100001  |

|          | 9       | 0001001 | 000 | 101 | 000     | 00     | 00     | 0001010 |

|          | 10      | 0001010 | 111 | 000 | 000     | 00     | 00     | 100000  |

|          | 11      | 0001011 | 000 | 000 | 000     | 00     | 00     | 1000000 |

| EXCHANGE | 12      | 0001100 | 000 | 000 | 000     | 01     | 01     | 1000011 |

|          | 13      | 0001101 | 001 | 000 | 000     | 00     | 00     | 0001110 |

|          | 14      | 0001110 | 100 | 101 | 000     | 00     | 00     | 0001111 |

|          | 15      | 0001111 | 111 | 000 | 000     | 00     | 00     | 100000  |

| FETCH    | 64      | 1000000 | 000 | 000 | 000     | 00     | 00     | 1000001 |

|          | 65      | 1000001 | 000 | 100 | 000     | 00     | 00     | 1000010 |

|          | 66      | 1000010 | 000 | 000 | 000     | 00     | 11     | 0000000 |

| INDRCT   | 67      | 1000011 | 000 | 100 | 000     | 00     | 00     | 1000100 |

|          | 68      | 1000100 | 000 | 000 | 000     | 00     | 10     | 0000000 |

## Partial Binary Microprogram

|                 | -          |          |           | ruth 7<br>nmed |             |        |                |

|-----------------|------------|----------|-----------|----------------|-------------|--------|----------------|

| <u>BR Field</u> |            | Inpu     | <u>.t</u> | <u>M</u>       | <u>UX 1</u> | Load a | <u>SBR</u>     |

|                 | <u>I</u> 1 | <u>I</u> | T         | <u>S</u> 1     | <u>S_0</u>  | L      |                |

| 0 0             | 0          | 0        | 0         | 0              | 0           | 0      | Next address   |

| 0 0             | 0          | 0        | 1         | 0              | 1           | 0      | Specified addr |

| 0 1             | 0          | 1        | 0         | 0              | 0           | 0      |                |

| 0 1             | 0          | 1        | 1         | 0              | 1           | 1      |                |

| 1 0             | 1          | 0        | x         | 1              | 0           | 0      | Subroutine ret |

| 1 1             | 1          | 1        | X         | 1              | 1           | 0      | Ext. addr.     |

| 1 0             | 1          | 0        | X         | 1              | 0           | 0      |                |