# Computer Organization and Assembly Language

Lecture 2 – x86 Processor Architecture

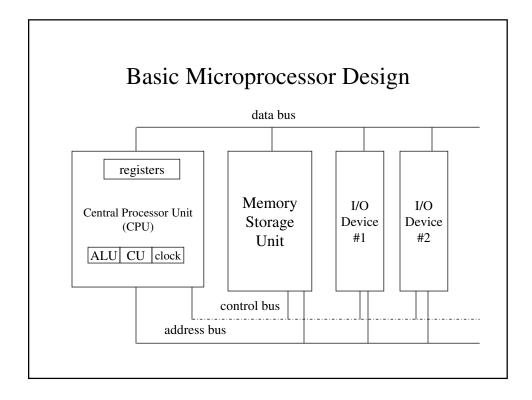

- CPU (*C*entral *P*rocessing *U*nit) or Processor - is the brain of the computer.

- In the PC, the Processor is in the Intel 80x86 or Pentium family.

# **Reading From Memory**

- Memory access is an important factor in understanding program execution speed because memory access via the system bus is much slower than the CPU clock.

- The clock cycles that are wasted while waiting for operands to be fetched are called *wait states*.

## Cache Memory

- Cache memory saves data received fetched from or written to memory. Since it is much faster than conventional memory, there are fewer wait states.

- Level-1 cache is built into the processor.

- Level-2 cache is located on separate chips near the processor.

## Multitasking

- An operating system that can run more than one process (or task) at once is called *multitasking*.

- Since most computers have only one processor, they multitask by giving each process a small portion of processor time called a *time slice*.

- The computer must be able to switch processes quickly, which means that they can store the process's state before switch.

- Round-robin scheduling is a typical scheduling algorithm where there is a strict rotation between the active processes.

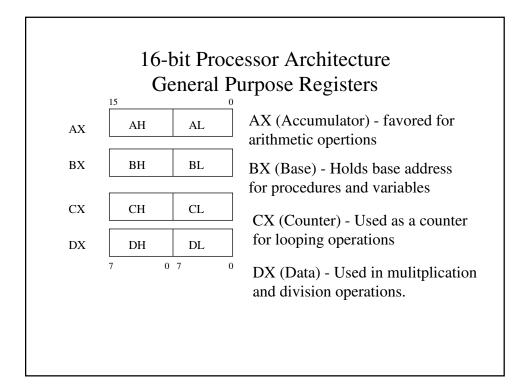

|        | 32-bit I           | Register |  |

|--------|--------------------|----------|--|

| 31     | General Purpose    | Index    |  |

| EAX    | AX                 | EBP      |  |

| EBX    | BX                 | ESP      |  |

| ECX    | СХ                 | ESI      |  |

| EDX    | DX                 | EDI      |  |

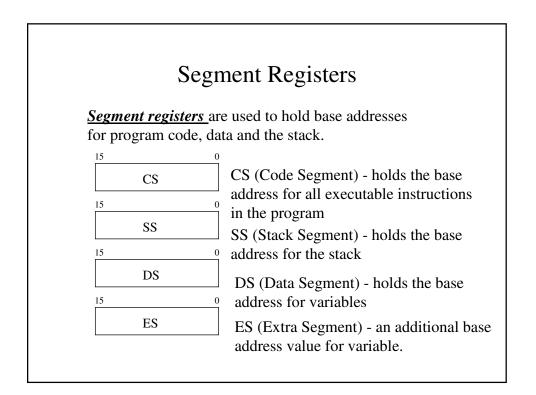

|        |                    | Segment  |  |

|        | Status and Control | CS       |  |

| EFLAGS | Flags              | SS       |  |

| EIP    | IP                 | DS<br>ES |  |

|        |                    | FS       |  |

|        |                    | GS       |  |

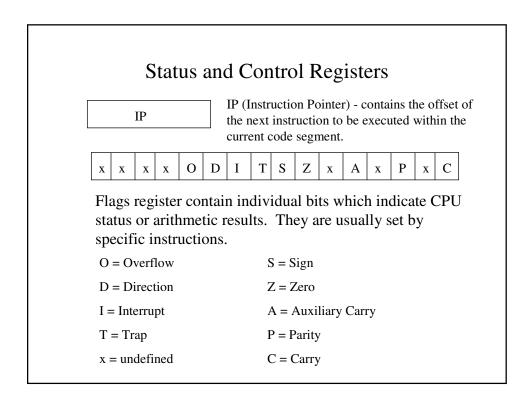

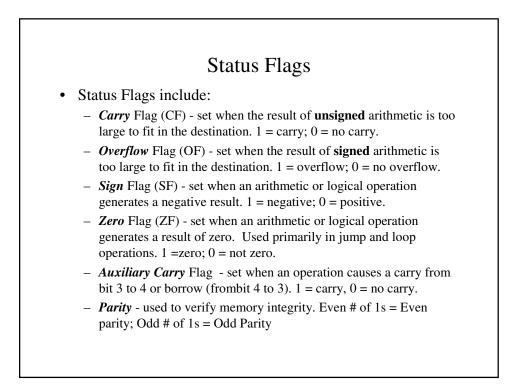

#### Flags

There are two types of flags: control flags (which determine how instructions are carried out) and status flags (which report on the results of operations.

Control flags include:

- *Direction* Flag (DF) affects the direction of block data transfers (like long character string). 1 = up; 0 - down.

- *Interrupt* Flag (IF) determines whether interrupts can occur (whether hardware devices like the keyboard, disk drives, and system clock can get the CPU's attention to get their needs attended to.

- *Trap* Flag (TF) determines whether the CPU is halted after every instruction. Used for debugging purposes.

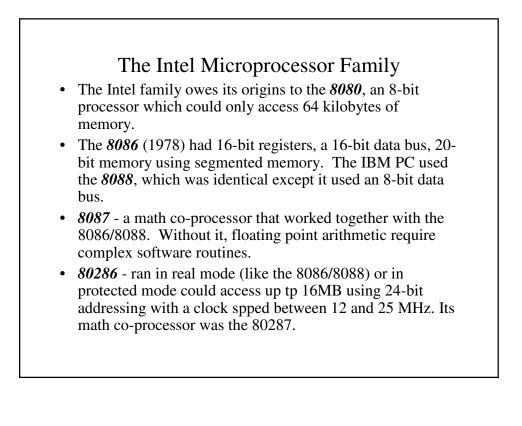

### The Intel Microprocessor Family (continued)

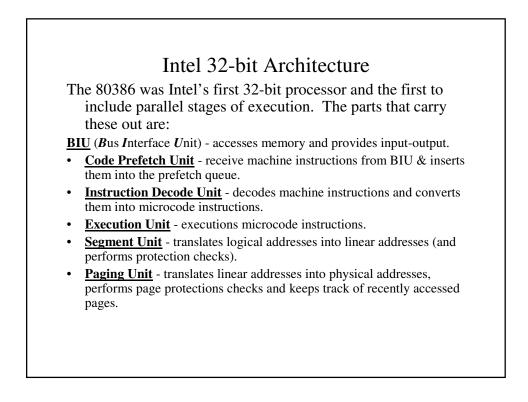

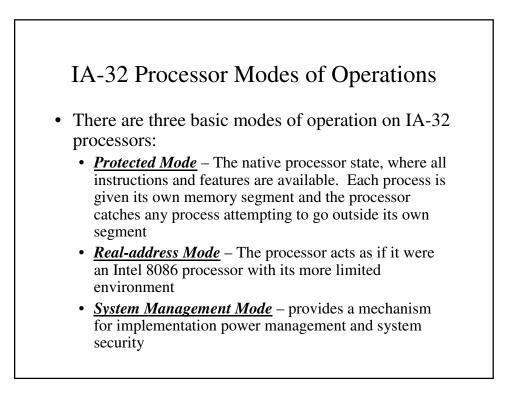

- 80386 or *i386* (1985) used 32-bit registers and a 32-bit data bus. It could operate in real, protected or virtual mode. In virtual mode, multiple real-mode programs could be run.

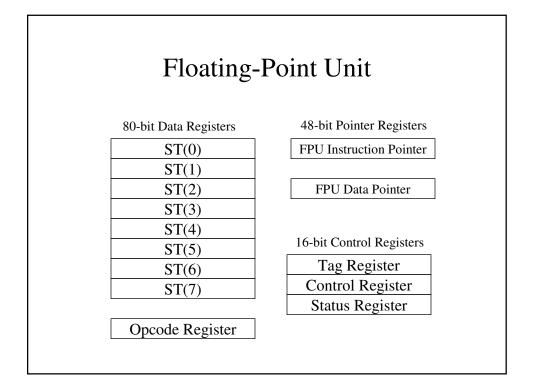

- *i486* The instruction set was implemented with up to 5 instructions fetched and decoded at once. SX version had its FPU disabled.

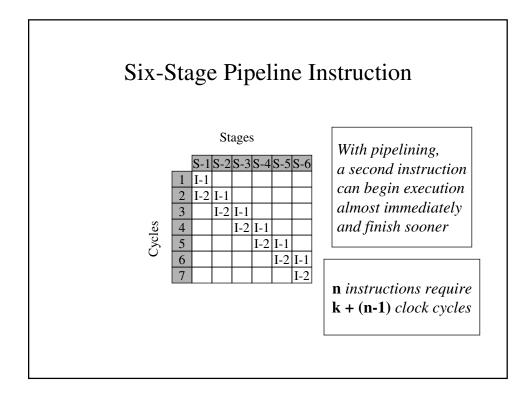

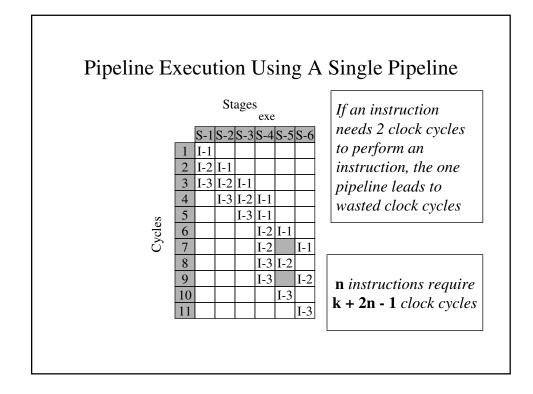

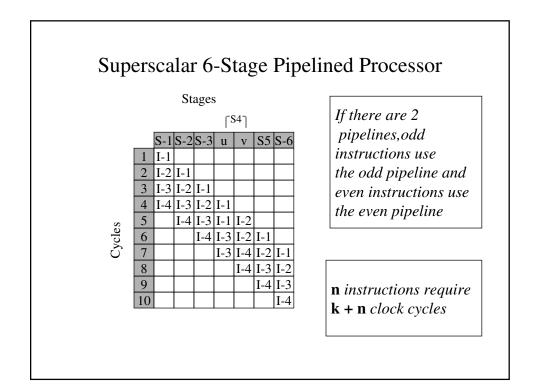

- The Pentium processor had an original clock speed of 90 MHz and cold decode and executed two instructions at the same time, using *dual pipelining*.

# Intel Core Processor Family

- Intel introduce the Core family of processors in 2006, which are more powerful than the Pentium processors that preceded them.

- So far they include:

- Core 2 Duo 2 processors codes, 1.8-3.3 GHz, 64 bit, 6 MByte L2 cache.

- Core 2 Quad 4 processors codes, up to 12 MByte L2 cache, 1333 MHz front side bus.

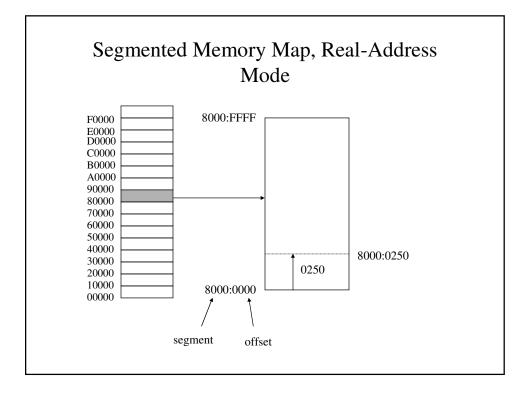

| Calculatin                                | g Absolute Addresses                                                                                 |

|-------------------------------------------|------------------------------------------------------------------------------------------------------|

|                                           | emory has its own address, with<br>om 0 up through highest memory                                    |

| e v                                       | sed in instructions) and physical<br>ata and instructions are stored) are not<br>ranslation process. |

| • There are two hexad                     | ecimal formats used used by Intel                                                                    |

| processors:                               |                                                                                                      |

| – 32-bit segment-offse                    | t address (e.g.,08F1:0100)                                                                           |

| <ul> <li>20-bit absolute addre</li> </ul> | ess (e.g., 09010)                                                                                    |

| Segment value:                            | 0 8 F 1 (0)                                                                                          |

| Offset:                                   | 0 1 0 0                                                                                              |

| Absolute address                          | 09010                                                                                                |

## The Motherboard

- The motherboard has connections to all or most of the following:

- CPU

- External cache memory

- Main memory SIMMs or DIMMs

- ROM BIOS

- IDE cables (for hard disks and CD-ROM drives)

- Sound synthesizers

- Parallel, serial, USB, video, keyboard, joystick, and mouse connections

- Network adapters

- PCI Bus Connectors for sound cards, graphics cards, data acquisition boards and other I/O devices.

## Video Output

- The video adapter control the display of both text and graphics.

- The video adapter consists of:

- the video controller, which is a special-purpose microprocessor which controls what appears where on the screen.

- video display memory, which stores what is displayed where on the screen.

- All text and graphics is stored in video RAM and sent to the monitor via the video controller.